# Investigation of gated mode operation of the Belle II pixel detector

Jan Cedric Hönig

Masterarbeit in Physik angefertigt im Physikalischen Institut

vorgelegt der Mathematisch-Naturwissenschaftlichen Fakultät der Rheinischen Friedrich-Wilhelms-Universität Bonn

Oktober 2016

I hereby declare that this thesis was formulated by myself and that no sources or tools other than those cited were used.

Bonn, .....Date

Signature

Gutachter: Prof. Dr. Jochen Dingfelder

Gutachter: Prof. Dr. Klaus Desch

# Contents

| 1 | Introduction 1          |                                                    |   |  |  |  |  |  |

|---|-------------------------|----------------------------------------------------|---|--|--|--|--|--|

|   | 1.1                     | A short history of insights                        | l |  |  |  |  |  |

|   | 1.2                     | The Belle II detector   3                          | 3 |  |  |  |  |  |

| 2 | The                     | The Belle II pixel detector 5                      |   |  |  |  |  |  |

|   | 2.1                     | DEPFET pixel                                       | 5 |  |  |  |  |  |

|   |                         | 2.1.1 Charge collection in DEPFET                  | 5 |  |  |  |  |  |

|   |                         | 2.1.2 Charge removal from DEPFET                   | 7 |  |  |  |  |  |

|   | 2.2                     | DEPFET matrix                                      | 3 |  |  |  |  |  |

|   | 2.3                     | The DEPFET half ladder                             | ) |  |  |  |  |  |

|   | 2.4                     | Gated mode                                         | ) |  |  |  |  |  |

|   | 2.5                     | Radiation damage    11                             | Ĺ |  |  |  |  |  |

| 3 | Test setup 13           |                                                    |   |  |  |  |  |  |

|   | 3.1                     | Hybrid 5 board                                     | 3 |  |  |  |  |  |

|   |                         | 3.1.1 DHP                                          | 1 |  |  |  |  |  |

|   |                         | 3.1.2 Switcher                                     | 1 |  |  |  |  |  |

|   |                         | 3.1.3 Drain Current Digitizer                      | 5 |  |  |  |  |  |

|   | 3.2                     | DHE and DHH                                        | 5 |  |  |  |  |  |

|   | 3.3                     | Software                                           | 5 |  |  |  |  |  |

|   | 3.4                     | Laser scan                                         | 5 |  |  |  |  |  |

| 4 | DCD-optimisation 19     |                                                    |   |  |  |  |  |  |

|   | 4.1                     | The Drain Current Digitizer readout ASIC           | ) |  |  |  |  |  |

|   |                         | 4.1.1 The CMC                                      | ) |  |  |  |  |  |

|   | 4.2                     | General analogue to digital conversion             | l |  |  |  |  |  |

|   |                         | 4.2.1 Differential nonlinearity                    | 2 |  |  |  |  |  |

|   |                         | 4.2.2 Integral nonlinearity 23                     | 3 |  |  |  |  |  |

|   | 4.3                     | Method of optimisation                             | 3 |  |  |  |  |  |

|   | 4.4                     | Measurements                                       | 5 |  |  |  |  |  |

|   |                         | 4.4.1 First parameter sweep: IPSource vs IPSource2 | 5 |  |  |  |  |  |

|   |                         | 4.4.2 Second parameter sweep: AmpLow vs RefIn      | 3 |  |  |  |  |  |

|   |                         | 4.4.3 Iterative parameter scan                     | ) |  |  |  |  |  |

| 5 | Irradiation campaign 31 |                                                    |   |  |  |  |  |  |

|   | 5.1                     | Optimising the AmpLow and Refin parameters         | l |  |  |  |  |  |

|   | 5.2                     | Optimising the IPSource and IPSource2 parameters   | 3 |  |  |  |  |  |

|   | 5.3                     | Continuous irradiation                             | 3 |  |  |  |  |  |

| 6               | Gated mode            |         |                                            |    |  |  |

|-----------------|-----------------------|---------|--------------------------------------------|----|--|--|

|                 | 6.1                   | Oscillo | oscope measurements                        | 37 |  |  |

|                 |                       | 6.1.1   | Normal readout                             | 37 |  |  |

|                 |                       | 6.1.2   | Gated mode operation                       | 37 |  |  |

|                 |                       | 6.1.3   | Time required to read out one gate         | 39 |  |  |

|                 |                       | 6.1.4   | DHE memory timing                          | 41 |  |  |

|                 |                       | 6.1.5   | DHP trigger line                           | 42 |  |  |

|                 | 6.2                   | Gated 1 | mode measurements with a laser             | 46 |  |  |

|                 |                       | 6.2.1   | Time required to go into gated mode        | 47 |  |  |

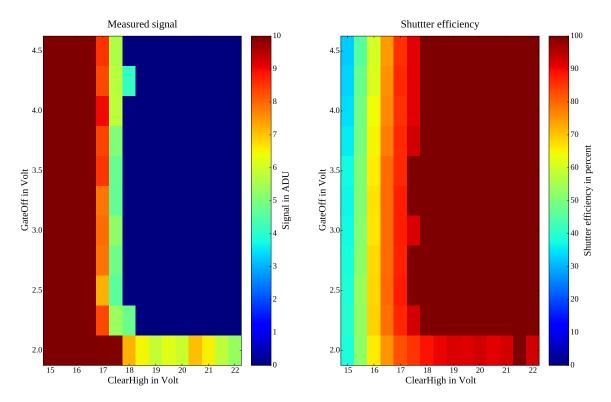

|                 |                       | 6.2.2   | GateOff-ClearHigh influence on gated mode  | 52 |  |  |

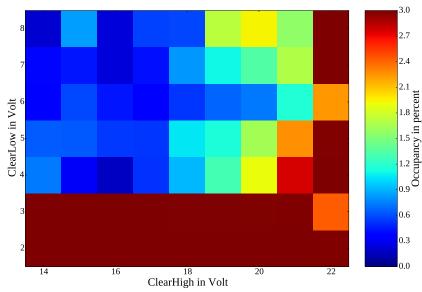

|                 |                       | 6.2.3   | ClearLow-ClearHigh influence on gated mode | 55 |  |  |

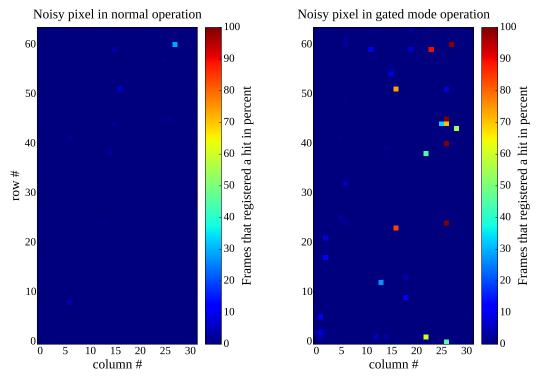

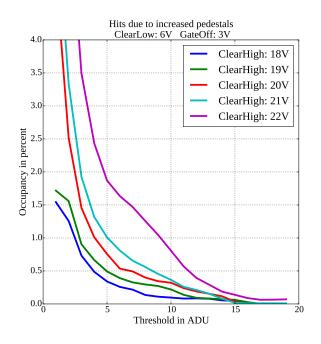

|                 |                       | 6.2.4   | Investigation of gated mode fluctuations   | 56 |  |  |

|                 |                       | 6.2.5   | Position-dependent measurements            | 59 |  |  |

| 7               | Summary and Outlook 6 |         |                                            |    |  |  |

| A               | Gated mode            |         |                                            |    |  |  |

| В               | Configuration         |         |                                            |    |  |  |

| References      |                       |         |                                            |    |  |  |

| List of Figures |                       |         |                                            |    |  |  |

| List of Tables  |                       |         |                                            |    |  |  |

# CHAPTER 1

# Introduction

Where do we come from? How was the universe created? Particle physicists have been researching to figure out answers to these questions. Curiosity was a driving factor for them, trying to understand the foundation our universe is built on, to see which fundamental forces govern the universe. The Standard Model of particle physics has been successful so far in describing and predicting interactions between particles. Great achievements have been made by particle physicists in the last decades, expanding and verifying the Standard Model. Nonetheless the current Standard Model is not flawless. It is unable to answer fundamental questions like how did the universe begin? Or why does the universe consist of matter? Thus new more precise experiments are conducted in an attempt to discover new physics, physics currently not contained in the Standard Model. As better and bigger particle accelerators are commissioned and built detectors need to advance as well to keep up with the new requirements.

## 1.1 A short history of insights

Every particle has its own antiparticle. If a particle interacts with its corresponding antiparticle, they annihilate. In the Fifties of the last century people believed that both particle and antiparticle are governed by the same laws. The common belief was that after mirroring charge and spatial coordinates (CP-symmetry), one would be able to apply the same laws to the antiparticles as to particles. Yet in the following years this belief was shaken when violations of this symmetry were discovered. After CP-violation in Kaon systems was observed by James Cronin and Val Fitch the year 1964, theoretical physicists struggled to explain this disparity [1]. It took nearly ten years until Kobayashi and Maskawa found the solution to this problem in 1972. They solved the problem of asymmetry by postulating the existence of two new elementary particles the top (t) and bottom (b) quarks [2]. With earlier work from N. Cabibbo this lead directly to the discovery of the Cabibbo–Kobayashi–Maskawa matrix (CKM matrix). The CKM matrix describes the strength and probability of flavour changing weak decays. This approach, which allowed them to integrate CP-violation into the Standard Model of particle physics, was the cue for a search for new particles. Finally, in 1977 the bottom quark was first observed at Fermilab, serving as a first step to verify their theories[3].

More than 30 years later, at the beginning of this century, large parts of the CKM matrix were well investigated, but scientists were still aspiring to prove the theories of Kobayashi and Maskawa completely. The final breakthrough arrived in the late 1990s when electron colliders which featured high luminosity were built. Two famous experiments which investigated CP-violation are the BaBar experiment in California and the Belle experiment in Japan. Their accelerators, the so-called B-factories, were designed to study CP-violation appearing in B mesons. These mesons are of interest because their lifetime, though

very short, is still comparatively long compared to other heavy mesons. If CP-symmetry was preserved, one would expect B and  $\overline{B}$  mesons to have the same lifetime. To detect even slight differences in lifetime very precise measurements of the lifetime were necessary (further information on B-factories can be found in [4]).

Within the framework of the Belle experiment electrons and positrons are collided with a centre of mass energy of 10.579 GeV. This is equivalent to the mass of the  $\Upsilon(4S)$  resonance, which consists of a **b** and  $\mathbf{\bar{b}}$  quark. The  $\Upsilon(4S)$  decays into B-mesons consisting of a **b** and a **u** or **d** quark. The lifetime of B mesons is in the order of  $(1.519\pm0.007)\cdot10^{-12}$ s[5]. This lifetime causes B mesons to decay before they enter the detector, which makes detection by conventional methods difficult. In order to work around this problem different energies for electron and positron beams are used. The positron beam is accelerated up to 3.5 GeV while the electron beam is accelerated up to 8 GeV[6]. This way the created mesons are boosted in direction of the electron beam. Instead of measuring the lifetime directly it becomes possible to measure the distance travelled by the mesons and deduct their lifetime from this information. A difference in the distances travelled by the meson and antimeson can be translated to a different lifetime and thus a violation of CP symmetry. There are plans for a follow-up experiment which will be called Belle II experiment. This follow-up experiment comes with a drastic increase in peak luminosity of the KEKB accelerator from  $2.108 \times 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>[7] to a design value of  $8 \times 10^{35}$  cm<sup>-2</sup> s<sup>-1</sup> ([8] p.21). Furthermore the KEKB accelerator will be upgraded and renamed to SuperKEKB. By comparison the design luminosity at LEP (Large Electron-Positron Collider), which was optimised for high energies rather than luminosity, was only  $16 \times 10^{30}$  cm<sup>-2</sup> s<sup>-1</sup> ([9] p.2). This upgrade of the accelerator and especially the increase in luminosity will make a complete redesign of the Belle detector mandatory. One performance measure in detectors is vertex resolution<sup>1</sup>. Being able to distinguish secondary vertices of particles with a short lifetime from the primary vertex is a requirement for the Belle II vertex detector. With the redesigned modern Belle II detector it could become possible to look for new physics in loop processes in SuperKEKB, due to the large luminosity even rare decays could be studied with a sufficient number of events. Furthermore studies at SuperKEKB could discover new particles which appear in heavily suppressed decays. Finally the discovery of new physics is expected of current experiments at large hadron accelerators like the LHC in CERN. The new SuperKEKB accelerator could serve to

secondary vertices is crucial. An important part of modern vertex detectors is the pixel detector. Pixel detectors offer good intrinsic resolution<sup>2</sup>, while being able to cope with high amounts of ionising radiation and the ensuing high occupancy. Thus the innermost layer of particle detectors is often made of pixel detectors. In the redesign of the Belle detector a pixel detector will be added. The Belle II detector will use the **D**Epleted **P**-Channel Field Effect Transistor (DEPFET)[10] technology. In section 2 this work will discuss what a pixel detector is in and in section 2.1 elaborate details of the DEPFET technology. The research part of this thesis is further divided in two parts. Chapters 4 and 5 will deal with optimising the electronics connected to DEPFET. While chapter 6 will investigate a new mode of operation for DEPFET.

investigate these events with high statistics. One of the goals of Belle II is to research particles with a short lifetime. To research these kinds of particles the ability to distinguish the interaction point from

<sup>&</sup>lt;sup>1</sup> A vertex is the point in space where particles, in case of the KEKB accelerator electrons and protons, collide. This point is also called primary vertex or interaction point. When particles are created displaced from the primary vertex, this point is called secondary vertex. A secondary vertex occurs when a particle created in the primary vertex decays.

$<sup>^{2}</sup>$  Intrinsic resolution indicates how well a detector can resolve where it has been hit.

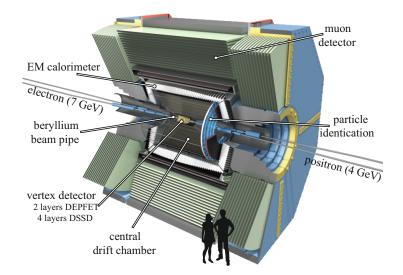

## 1.2 The Belle II detector

The Belle II detector is built in layers. Each layer is responsible for acquiring different information about the particles passing the detector. A superconducting solenoid magnet creates a magnetic field of roughly 1.5 T to bend the tracks of charged particles passing the detector. The different layers in the Belle II detector include, starting from the outermost layer moving to the interaction point:

- $K_L$  and muon detector (KLM): This part of the detector is responsible for detecting  $K_L$  (long kaons) and  $\mu$  (muon). While muons do not interact strongly and do not lose enough energy to be stopped in the detector,  $K_L$  create hadronic showers in this detector and are stopped here.

- **Electromagnetic calorimeter (ECL):** Most particles created in Belle II are stopped in this part of the detector. It measures mass and energy of electromagnetically interacting particles.

- **Particle identification system (PID):** This part of the detector is mainly responsible for differentiation between kaons and pions. It relies on Cherenkov light to accomplish this.

- **Central drift chamber (CDC):** This part of the detector is filled with gas. When a charged particle passes it creates electron-ion pairs, which when attracted to charged wires create particle cascades. Furthermore the CDC is responsible for tracking, momentum measurement and triggers the VXD.

- Silicon vertex detector (VXD): The innermost part of the detector is mainly responsible for distinguishing primary and secondary vertices. Furthermore hits are used for a precise track reconstruction close to the interaction point.

Figure 1.1: Sketch of different layers of the Belle II detector [11].

#### Vertex detector performance

The important parameters for the vertex resolution can be understood from a simple two-layer detector model. The vertex resolution ( $\sigma_{vertex}$ ) of such a detector with two layers, with layer 1 being the inner and

layer 2 the outer layer, is described by ([12] p.272):

$$\sigma_{\text{vertex}} = \left(\frac{r_1}{r_2 - r_1}\sigma_2\right)^2 + \left(\frac{r_2}{r_2 - r_1}\sigma_1\right)^2 + \sigma_{\text{MS}}^2.$$

In this formula  $r_1$  is the distance between inner layer and beam line and  $r_2$  is the distance between the outer layer and the beam line. The variable  $\sigma_1$  and  $\sigma_2$  are the intrinsic resolutions of the inner and outer layer. Finally  $\sigma_{MS}$  represents the decrease in resolution due to multiple scattering.

The effects of multiple scattering are proportional to the material budget ( $\sigma_{MS} \propto 1/\sqrt{x/X_0}$ ). The parameters with the strongest influence on the vertex resolution are the distance of the innermost layer from the interaction point ( $r_1$ ), the intrinsic resolution of the innermost layer ( $\sigma_1$ ) and the material measured in radiation lengths ( $x/X_0$ ). In addition, a higher number of detector layers provides more interaction points and better track reconstruction.

#### The Belle II vertex detector

To allow for precise vertex reconstruction the Belle II vertex detector has six layers of two different silicon detector technologies. The two innermost layers are DEPFET pixel detectors and the four outermost layers are strip detectors called DSSD (Double-Sided Silicon Strip Detector). Strip detectors allow for excellent spatial resolution (in the case of the Belle experiment strip pitches of 22.5 to 76  $\mu$ m ([13] p.3)) and good time resolution (shaping time of 1  $\mu$ s ([14] p.132). A downside to the strip technology is that it is challenging to deal with multiple hits. If more than one particle hits the detector at once the position of the hit becomes ambiguous and ghost hits appear<sup>3</sup>, hit to track association becomes difficult. In the Belle experiment the length of one strip was fairly large with strip length of 25.6 to 77.7 mm([13] p.3). That is why closest to the interaction point a pixel detector (PXD) will be used in the Belle II experiment (definition see section 2). PXD layers will be placed at a distance of 14 mm and 22 mm ([8] p.78). Pixel detectors have more readout channels and the small size of pixels makes multiple hits in one read out channel less likely. This makes it possible to place them closer to the interaction point. Strip detectors are placed at the outer layers of VXD. The DSSD will be placed at an inner radius of 38 mm and an outer radius of 140 mm from the interaction point ([8] p.139).

The pixel sensor type used in Belle II is called DEPFET. Due to the large number of read out channels DEPFET and pixel detectors in general produces large amounts of data. The pixel detector used in this thesis is produces data rates of up to 1.28 Gbit/s ([15] p.12). The total data rate produced by the PXD is expected to amount to up to 58 Gbit/s in the Belle II experiment. To reduce the data stream the 4 layers of DSSD are used. Because their environment is less severe and their integration time is lower than that of DEPFET they can be used to define regions of interest for the innermost two pixel detector layers. As especially the pixel detector to be as thin as possible. This prevents multiple scattering which leads to measurement errors in the other layers of the tracking detector. This thesis investigates properties of the DEPFET pixel detector.

<sup>&</sup>lt;sup>3</sup> Further information on the advantages and disadvantages of strip technology can be found in [12].

# CHAPTER 2

## The Belle II pixel detector

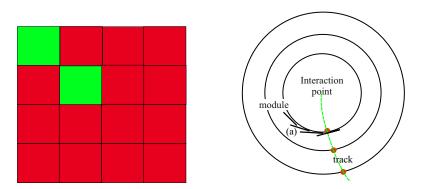

Figure 2.1: To the right, many detector modules (a) are positioned circularly around the interaction point. A particle passes the detector. On the left is a schematic picture of a pixel matrix. The green squares show which pixel cells in the grid recorded a hit. The information which pixels have been hit allows particle track reconstruction.

A pixel detector is a device used for position dependent measurements. The basic idea is to align a large number of individual pixel sensors to a grid. Those grids of particle detectors are placed circularly around the interaction point covering as much of the full 360° angle as possible, to leave the least space possible for particles to leave the detector undetected. Figure 2.1 displays such a pixel detector and how the information from pixel detectors is used for track reconstruction.

In a pixel detector each pixel is a fully functional sensor. The simplest type of silicon pixel sensor is a pn-diode. If a large enough reverse voltage is applied, the sensor is fully depleted, and very little current flows. But an ionizing particle passing through the detector will deposit energy which will result in the creation of electron hole pairs. These electron hole pairs will move according to the field created by the depletion voltage which will result in a current pulse. Measuring this current pulse provides information on how much energy has been deposited and when the ionizing particle interacted with the sensor.

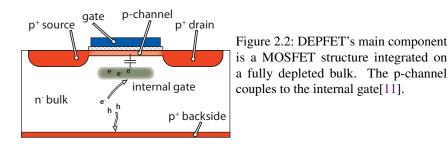

## 2.1 DEPFET pixel

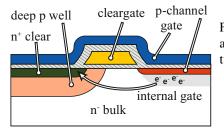

The **DE**pleted **P**-Channel Field Effect Transistor (DEPFET) is a silicon based detector. DEPFETs foundation is a p-channel MOSFET structure integrated on a fully depleted n-type silicon bulk. Below the MOSFET structure, just separated by a few micro meters from the external gate, is a strong  $n^+$  implantation, the so called internal gate.

A charged particle passing through the detector will create electron hole pairs. Holes will be attracted to the  $p^+$  backside, while electrons will be attracted to and collected inside the internal gate. The internal gate couples to the p channel by inducing mirror charges. These mirror charges change the width of the p-channel. Thus the amount of collected charge in the internal gate has an influence on the transistor current and measurements of the transistor current will yield information on the amount of collected charge. The coupling between internal gate and p-channel causes an internal amplification of the signal. The technique of internal amplification allows for excellent signal to noise ratio. The whole process is displayed in figure 2.3. As the readout in DEPFET is non destructive charge stored inside the internal gate can be sampled any time, so charge does not need to be measured as soon as it is created. Furthermore no read out electronics need to be placed directly on top of DEPFET. Thus the detector can be build more thinly and as the readout electronics, which need active cooling, are located outside the acceptance region, gas injection cooling is sufficient to dissipate the heat generated by DEPFET [16].

### 2.1.1 Charge collection in DEPFET

The internal gate is a strong  $n^+$  implantation right below the external gate. When in operation the complete DEPFET sensor is depleted. Depletion causes the internal gate to become positively charged. Thus the internal gate forms a potential minimum and is attractive for free electrons.

Due to the high luminosity in the Belle II experiment, the DEPFET detector needs a fast integration time. This also has an influence on charge collection. Charge needs to be collected before the next readout is done. But with the potential minimum created by the internal gate as the only mechanism for charge collection charge which is created at the edges of the pixel might not be collected in time before the next readout. Furthermore, charge created close to the edges might travel to a different pixel. As electrons diffuse until they reach a field with sufficient strength and drift to an internal gate. In conclusion just relying on the internal gates attraction to collect all electrons within the bulk is not enough. For that reason, mechanisms for quick and reliable charge collection are implemented in DEPFET. These mechanisms are sidewards depletion and a drift voltage.

#### Sidewards depletion

Figure 2.3: Depletion regions from top and bottom of the detector overlap close to the top, forming a potential minimum. [11]. If one wants to be able to create free charge carriers within the DEPFET, the bulk needs to be depleted. If one were to deplete a DEPFET pixel from one side, all newly created charge would be extracted from that contact. However, for DEPFET free charge carriers should go to the internal gate. That is why DEPFET is depleted from two sides using the so called sidewards depletion. Prerequisite are two p contacts at the top and bottom of the pixel and an additional n contact placed close to the edge of the pixel. The two p contacts are set on a potential which is negative in regard to the n contact. Depleted areas start to form around both p contacts. If their voltages are chosen high enough these two depleted areas will overlap, forming a potential minimum. This potential minimum can be moved within the pixel depending on how much larger or smaller one of the two voltages is compared to the other. If this potential minimum is moved to the same height as the internal gate it assists charge collection.

#### Drift voltage

Charge created in border areas of a pixel takes longer to drift to the internal gate than charge created in more central regions. To ensure all charge is collected in the short time between readout cycles, an additional drift voltage is implemented. This drift voltage is applied close to the edges of each DEPFET pixel. It is a negative voltage which pushes electrons closer to the central region of the DEPFET pixel. This also decreases the chance of electrons drifting to neighbouring pixels.

#### 2.1.2 Charge removal from DEPFET

Figure 2.4: Clear contact, clear gate and a deep p implant form a MOSFET structure[11].

Over time leakage currents and more and more charged particles interacting with the detector, would start filling the internal gate. This would continue until the internal gate is completely filled with electrons. The consequence being the loss of attraction to free charge carriers. Hence a mechanism is needed to remove charge from the internal gate. In DEPFET a process called clear is used to remove the collected charge from the internal gate and any leftover charge in the detector. Two additional contacts are required for the clear. One contact is the clear contact, which is used to extract charge from the DEPFET pixel. This contact is realised in form of a  $n^+$  implant. To prevent charge from travelling to the clear contact instead of the internal gate, during charge collection or read out, the clear contact is shielded by a deep p implant. The second contact is called clear gate. Together with the internal gate, deep p implant and clear contact, the clear gate forms a MOSFET structure. This MOSFET structure is reverse-biased to prevent any charge being lost within the clear contact. To clear a DEPFET pixel a large positive voltage is applied to the clear contact. Simultaneously the external gate is switched to on. This lowers the potential barrier between internal gate and clear. As a result, charge is able to punch through the potential barrier created by the deep p implant. The required contacts are displayed in the schematic in figure 2.4.

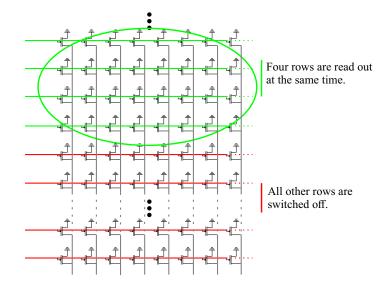

Figure 2.5: Rolling shutter readout of a DEPFET matrix. Simplified sketch, no drain lines are shared between pixels which are read out at the same time.

### 2.2 DEPFET matrix

In order to reduce material budget and decrease the amount of data generated, the DEPFET detector is not read out as a whole. Rather DEPFET employs a slightly modified rolling shutter mode. In a simple rolling shutter mode pixels are read out row by row, starting from the top. In this readout scheme there can only be one active row, all other rows must be switched off. This allows a reduction of the number of drain lines required to read out the pixel, because each column can share one drain line. The advantage of this readout scheme is that the material budget created by cables is drastically reduced. The downside of this readout scheme is speed. Compared to reading out the matrix directly, the full integration time of the matrix is much longer and given by the number of rows multiplied by the time required to read out one row ( $t_{tot} = N_{row} \times t_{1row}$ ).

The rolling shutter mode used in DEPFET is a slightly modified version of the simple rolling shutter mode. Instead of reading out row by row, DEPFET reads out four rows at once. This allows for reasonable integration times in the order of 20 µs [17] while keeping material budget and power consumption to a minimum ( $t_{tot} = \frac{N_{row}}{4} \times t_{1row}$ ). DEPFETs rolling shutter mode is displayed in figure 2.5. To integrate the matrix each pixel follows the ensuing algorithm:

**Charge collection phase:** 1. Gate voltage is set to a positive value (off state).

2. The detector starts collecting charge in the internal gate.

**Sampling phase:** 1. Gate voltage is set to a negative value (on state).

- 2. Wait until the current in the drain contact has settled.

- 3. Sample the drain current.

- 4. Raise voltage on the clear contact, to remove charge from the internal gate.

- 5. Lower clear voltage to allow charge collection to begin anew.

During the charge collection phase the detector is sensitive for incoming particles. While during the sampling phase the amount of electrons within the internal gate is measured. The matrix is read out and

cleared continuously, so after a fixed amount of time each pixel is read out. It is of special importance to choose the sampling point well. If the signal is measured too early the pixel's drain current might not have settled yet, if measured too late there is a risk of measuring during or after the clear. If the sampling point is chosen correctly, the drain current depends solely on the number of electrons stored in the internal gate. The change of current for a given change in number of electrons stored within the internal gate is called gain. The gain can be calculated with:

$$g_q = \frac{\partial I}{\partial q}.$$

In my bachelor thesis I determined the gain of a PXD 6 matrix to be  $(431 \pm 4) \text{ pA/e}^- \text{ h-pair}$ . For further explanation on how to obtain gain see [18]. The matrix used in this thesis is a PXD 9 Belle II prototype.

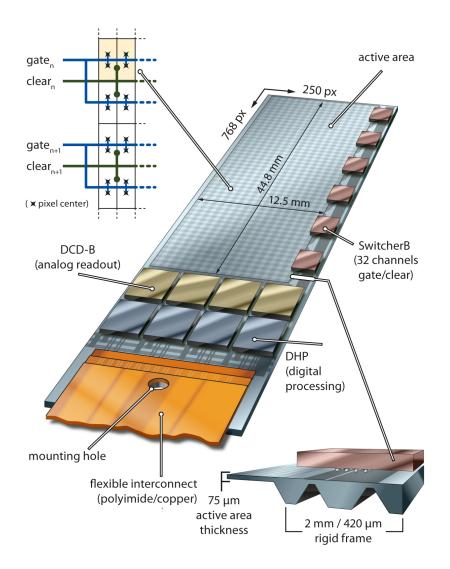

### 2.3 The DEPFET half ladder

In the Belle II experiment the DEPFET matrices will be organized in modules. The DEPFET modules for the Belle II pixel detector are entities that combine an active area with DEPFET pixels with the required steering and readout chips on one module. Figure 2.6 shows a half ladder featuring an array of  $250 \times 768$  pixels. The steering **a**pplication-**s**pecific **i**ntegrated **c**ircuits (ASICs) are bump-bonded at the side of the stave, while the readout ASICS are placed at the end of the module. The ASICs used in the module are:

- **Switcher:** The Switcher chip is responsible for selecting the active row. Gate and clear voltages are controlled with the Switcher.

- **DCD:** The Drain Current Digitizer (DCD) is responsible for converting the output signal of the matrix to a digital signal.

- **DHP:** The Data-Handling-Processor (DHP) is responsible for data reduction, buffering of data and steering and synchronisation of the other ASICs.

Four rows of the DEPFET matrix in the half ladder are connected to one electrical row (gate) of the Switcher forming 192 gates. Altogether six Switchers are used to steer the matrix. Thus each Switcher has 32 gate and clear outputs.

A half ladder has 4 DCDs with 256 input channels each, which send the digitized data to 4 DHPs for further processing.

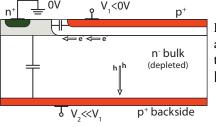

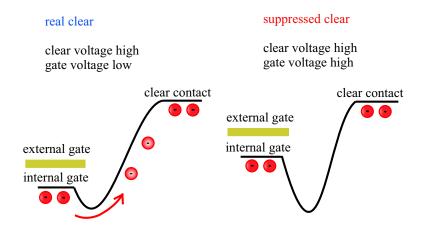

## 2.4 Gated mode

The improved superKEKB accelerator will use a continuous injection scheme. Every 20 ms [17] a  $e^+$  or  $e^-$  bunch will be refilled. The newly injected particles will produce large background and need roughly 3 ms [17] to cool down. The background is caused by the smeared out momentum of newly injected particles. These newly injected particles oscillate around the ideal bunch position or they are lost completely, creating signal while they pass the detector. This poses a special challenge because the integration time of DEPFET is in the order of 20 µs while bunches pass the interaction region every 10 µs [17]. This background from newly injected bunches coupled with the high data rates from the high luminosity could potentially lead to the detector data becoming unreliable and faulty. In order to make the DEPFET detector blind while these noisy bunches pass by a new mode of operation was suggested. This new mode will be called gated mode. Goal of this mode of operation is to suspend normal charge

Figure 2.6: A half length silicon module from the inner layer of the PXD[11].

collection whenever a noisy bunch passes the detector. Gated mode is based on the clear process of DEPFET. To put a pixel into gated mode the voltage at the clear contact is raised to a high voltage. At the same time the external gate is switched to off state. This maintains a potential barrier which charge from the internal gate cannot pass. On the other hand charge created in the bulk is not affected by this potential barrier and is extracted into the clear contact. Hence charge within the internal gate is preserved, while newly created charge is removed. This principle was proven to work in measurements by E. Prinker [19].

Switching the detector in and out of gated mode in a time frame which is lower than the integration time poses special challenges. The whole electronics chain needs to be flawless to not corrupt data. The timing for switching in and out of gated mode needs to be precise. Else there is a risk of measuring during the passage of a noisy bunch. Furthermore as few bunch crossings as possible should be gated, to measure as many physic events as possible. Thus optimising the electronics is a first step, before dynamic enabling and disabling of gated mode can be achieved.

Figure 2.7: In contrast to a normal clear in gated mode the external gate is turned off when clear is put to a high potential.

### 2.5 Radiation damage

When ionizing radiation enters a silicon lattice there are two ways it can interact with atoms. The radiation can interact with the electrons of the atoms, creating electron hole pairs in the process. The effects of this kind of interaction are reversible. The created electron hole pairs are what is measured in a silicon detector, they give information on the energy of the particle passing the detector. The other way radiation can interact with the atoms is by interacting with the nucleus (or the whole atom) directly. This can cause permanent changes to the silicon lattice.

The PXD will get irradiated by multiple processes which incluse synchrotron radiation and beam-gas Coulomb interactions. The main contribution to the background in the Belle II experiment will stem from fermions (mainly electrons and positrons)[20]. The main background stemming from the 4-fermion final state radiation:

$$e^+e^- \rightarrow e^+e^- + f^+f^-$$

This process is the main contribution to background, because being a quantum electrodynamic process it is luminosity dependent [21]. The dose rate at the experiment is luminosity dependent and is expected to be 5.4 kGy/year<sup>1</sup> for the outer layer of DEPFET and 20 kGy/year for the inner layer. Simulations and measurements predict that the damage done to the bulk will be small [20]. The largest effects will stem from surface damage. The radiation will create electron hole pairs in silicon dioxide layers. Silicon dioxide is used as an insulator in metal–oxide–semiconductors (MOS). In DEPFET the off voltage for the gate is positive. If the isolating silicon dioxide is irradiated electron hole pairs will form. The electrons are attracted to the positive gate voltage, while the holes move towards the silicon bulk.

However, the mobility of holes is much smaller than that of electrons. Thus, while electrons are swept out of the silicon dioxide in picoseconds, holes take seconds to travel to the silicon interface (at room temperature). There the holes form deep long-lived trap states, which can persist for hours or up to years [22].

The holes cause shifts in noise, threshold and transconductance [20].

<sup>&</sup>lt;sup>1</sup> One year is equal to the snowmass year of  $10^7$  s.

# CHAPTER 3

# **Test setup**

The following chapter describes the setup which was available to test the DEPFET system. The small testboard which houses the DEPFET matrix will be introduced. Furthermore the functionality of the FPGA board which is the link to the lab computer is explained. Finally a setup used for position dependent measurements will be described.

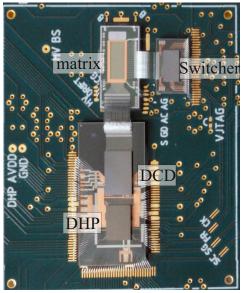

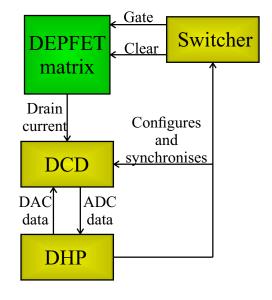

## 3.1 Hybrid 5 board

(a) Photo of Hybrid 5 components.

(b) Sketch of Hybrid 5 electronics.

Figure 3.1: Overview over Hybrid 5 electronics.

The DEPFET sensor used in this thesis was a short prototype consisting of  $64 \times 32$  DEPFET pixels. The small matrix is installed on a Hybrid 5 testboard. The Hybrid 5 board is a test board featuring ASICs similar to the ones which will be used in the final experiment. The Hybrid 5 board used in this thesis featured a single DHP, DCD and Switcher. The versions of the ASICs installed on the Hybrid 5 board

with the id H5.007, which was used in this thesis, are DHPT1.0, DCDBpp and Switcher B gated mode. The standard configuration which was used to operate the DEPFET matrix and ASICs can be found in table B.1 in the appendix. The Hybrid 5 board is connected to a custom-made power supply which was built at the LMU in Munich. It is able to provide all relevant voltages for the DEPFET sensor and ASICs. An overview over the components of the Hybrid 5 board is given in figure 3.1(a) and figure 3.1(b). This Hybrid 5 board is connected to a **D**ata-**H**andling-**E**ngine (DHE), which is the link to the lab computer, via two InfiniBand cables.

### 3.1.1 DHP

The DHP was designed in Bonn by T. Hemperek and H. Krüger[15]. The DHP is responsible for controlling the Switcher and DCD. Furthermore the data rate is strongly reduced in the DHP. To achieve this reduction of data rate the DHP only sends data when it is requested by a trigger signal. In addition, the data the DHP sends is zero suppressed. Meaning only information about pixels which show a signal significantly larger than their base signal is sent to the computer. The data reduction and noise filtering is done in three steps.

- 1. The base signal of all pixels, also called pedestal value, is subtracted from the measured signal. The pedestal values need to be measured and programmed into DHP memory beforehand.

- 2. Noise which affects all values of a gate, so called common mode noise, is filtered. This is done by using the two parse average method. In this method the average of all data values is computed. Large values are replaced with the average value. Then the average is calculated again. This average is the common mode and subtracted from all data in the measured gate.

- 3. The data which has been corrected for its base value and common mode noise is checked against a threshold. Information on the pixels above threshold is sent to the computer.

This data contains information on the measured values and position of all pixels above threshold. The data is tagged with information, if common mode correction, pedestal subtraction and threshold were applied. Furthermore information on the chip which measured the data and an ID in which readout frame the data was measured are sent.

The various registers of the DHP containing information on pedestals and other system variables can be configured using JTAG<sup>1</sup>. Commands choosing the mode of operation (gated mode or normal) as well as when to start the readout of the matrix from the top are received across a trigger line.

### 3.1.2 Switcher

The Switcher is responsible for controlling the gate and clear voltages of the DEPFET-Matrix. The Switcher has two high voltage switches for clear and gate voltages:

The high clear voltage is called ClearHigh and switches the clear on, the low clear voltage is called ClearLow and switches the clear off. The high gate voltage is called GateOff and switches the external gate off, the low gate voltage is called GateOn and switches the external gate on.

The Switcher has 32 gate and 32 clear lines, which can be used to control 128 matrix rows. In case of

<sup>&</sup>lt;sup>1</sup> Joint Test Action Group is a protocol which allows the prgramming and debugging of integrated circuits and computer chips directly within the circuit.

Hybrid 5 only 16 of those lines are connected. The rows in the DEPFET-Matrix are activated in a fixed order, which is controlled by a shift register which is running along rows. This shift register is controlled by a serial input (short: SerIn) which is connected to the DHP. When a logical one is put in SerIn, this one is the signal for the Switcher to start operation. Subsequently the logical one is clocked through the shift register, activating the rows in order.

The Switcher has two memory regions for readout sequences. The first memory region contains the normal readout sequence, the second one contains a gated mode sequence. If the Switcher receives the veto signal it switches into the second memory block. As soon as no veto signal is registered the Switcher goes back to normal readout. It resumes by reading out the gate which would have been read out, if the Switcher stayed in the first memory block for the full duration. The Switcher is located next to the DEPFET-Matrix at the side of the module, see figure 3.1(a).

### 3.1.3 Drain Current Digitizer

The **D**rain Current **D**igitizer (DCD) handles the conversion of analogue DEPFET-Matrix signals to digital signals. Each chip has 256 channels of which 128 are connected to the DEPFET-Matrix in case of Hybrid 5. The 128 channels are organized in 4 column pairs with 32 channels each. Each of these channels has an input dynamic range in the order of 16  $\mu$ A[23]. The signal is converted in an **a**nalogue **d**igital **c**onverter (ADC) with a precision of 8 bits. Which gives a total of 2<sup>8</sup>=256 ADC codes to work with. More details on the DCD will be explained in section 4.1.

## 3.2 DHE and DHH

The Data-Handling-Engine (DHE) is placed between computer and the Hybrid 5 board in the electronics chain. It is the link between the Software interface installed on the computer and the rest of the system. The DHE is responsible for generating the DHP system clock and controls the Hybrid 5 system with trigger signals. Those trigger signals are created with an 80 MHz clock by the DHE. Four trigger signals are created and sent to the Hybrid 5 board:

- **Frame sync:** Serves to synchronise frames<sup>2</sup> and is the signal for the DHP to start integration from the beginning.

- **Trigger:** Is the signal for the DHP to start sending data. The DHP only sends data, if it receives a trigger signal.

**Veto:** Is the signal to go into gated mode operation.

**Reset:** If the reset signal is sent the whole system is reset.

Those four signals are encoded in an 8 Bit Manchester code<sup>3</sup> and then transmitted to the DHP on a trigger line with 80 MBit/s. Thus, commands are transmitted with an effective speed of 10MHz. Hence, one expects a delay between command issue and completion. It is possible to program set sequences of trigger signal within the DHE. Length and timing of the different control signals within the DHE can be set in steps of the DHE reference clock. An adapter card for the DHE exists. This card allows it to read out the veto, frame sync and DHP trigger signals. In addition, the adapter card has a connector which allows for triggering of a laser with the DHE. This allows for programming of operation sequences in

$<sup>^{2}</sup>$  The package of data obtained after reading the full matrix out once is called frame.

<sup>&</sup>lt;sup>3</sup> In Manchester encoding a 1 is encoded as 10 and a 0 as 01. This way the arriving signal is DC-balanced by default.

which the laser is shot with precise timing relative to the internal operations of the system.

The DHE features its own current source, with a scope of  $248 \,\mu$ A which can be divided in 65000 steps. This current source can be used to inject currents into individual DCD channels. This gives the capability to observe the DCDs response to a known input current. Measurements using the DHE current source are used to optimise DCD parameters.

The DHE is part of the **D**EPFET **H**andling **H**ub (DHH). In the final experiment the DHH will contain multiple DHE, one for each module. The Hybrid 5 system used in this thesis only uses one DHE.

## 3.3 Software

The most important part of the Software framework are four Experimental Physics and Industrial Control System (EPICS) servers. These EPICS servers store the current state of the system. All parameters and voltages are stored inside process variables (PV). The parameters are linked directly to the DHE, power supplies and the Hybrid 5 board. If any value is changed in the server, the corresponding value in the part of the system is changed accordingly! Communication with the servers can be done directly from the linux terminal with the commands **caput**, to change a variable, and **caget**, to read out a variable. As a more convenient solution a widget collection was developed in CS-Studio which provides a graphic interface to access all important system parameters. The EPICS PVs can also be modified within a python script. A collection of python scripts exists within the collaboration. These scripts range from basic building blocks for creating more advanced scripts to scripts which can optimise some parameters of the system automatically. The DCD optimisation done in this thesis relied on a script which can be configured to probe a freely selectable number of DCD channels with previously chosen voltages and parameters.

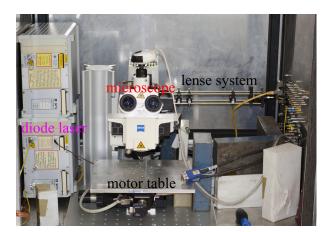

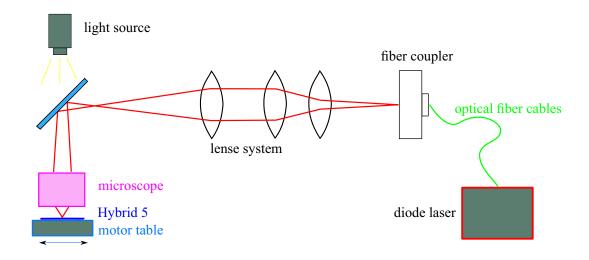

## 3.4 Laser scan

Figure 3.2: Content of the aluminium box.

With a laser scan position dependent measurements can be conducted. These scans can be used to verify the behaviour across large parts of the DEPFET matrix. The Hybrid 5 board is placed, with its back facing upwards, on top of a motor table. With the motor table position of the Hybrid 5 can be adjusted in steps of  $0.5 \,\mu\text{m}$ . The laser is triggered with a pulse generator. Laser pulse length, intensity and repetition rate can be controlled from the pulse generator. The pulse generator is set to fire the laser

as long as an external trigger is present, which is provided by the DHE adaptercard.

The laser light is directed to a fiber coupler with optical fiber cables. From there a system of lenses directs the light into a microscope. The microscope focuses the laser beam on the DEPFET matrix. It is possible to view the laser beam with the microscope and confirm the position of the laser beam on the matrix. Because DEPFET is sensitive enough to detect daylight the Hybrid 5 together with the laser, optical system and motor table are placed within an aluminium box of 1 m<sup>3</sup>. The pulse generator remains outside to allow access to the laser configuration. Figure 3.2 shows a photo of the system. In figure 3.3 a sketch of the important components for the laser scan is shown. Measurements are started from the computer.

Figure 3.3: Sketch of the laser setup (derivative of [24]).

With the computer laser pulse length can be controlled via the DHE adapter and the illuminated position via the motor table.

# CHAPTER 4

# **DCD-optimisation**

This chapter will explain how analogue signals are converted to digital signals in the DCD. Important parameters are introduced which indicate the quality of an analogue to digital conversion. Finally the DCD performance is optimised using the introduced methods.

## 4.1 The Drain Current Digitizer readout ASIC

The Drain Current Digitizer (DCD) is mounted right next to the matrix and responsible for digitizing the output signal of the matrix. The design of the current electronics called DCDBpp, able to cope with the ensuing high radiation and with the required sampling rate of 50MHz, was created by Ivan Perić [23]. Former versions of the DCD were designed as cyclic ADCs, but the version used in this thesis was a pipeline ADC.

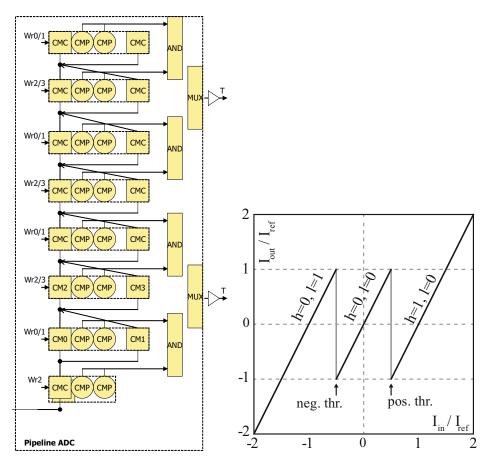

The pipeline ADC is sketched in figure 4.1 on the left and consists of blocks. Each of the blocks contains two Current Memory Cells (CMC) and two comparators. The current memory cells feature a reference current (R) which can be added or subtracted from the saved signal. DEPFET uses eight blocks in its DCD. Starting from block 0 the conversion is done as follows:

- **block 0:** The analogue signal from the detector is saved in both CMCs. The comparators are connected to the first cell. One comparator compares the signal to a high threshold (h), the other one to a low threshold (l). If the signal is larger than the high threshold, then the reference current is subtracted from the signal in both cells. Consequently if the current is smaller than the low threshold, the reference current is added. Finally, if the signal is in between thresholds nothing is changed. After altering the saved currents with the reference current, the sum of both CMCs currents is written in the first cell in block 1. Then roughly 20ns later the second cell in block 1 is set to the same value. As for the comparators they switch their output signals to one once their condition is fulfilled. Thus the output codes are for input currents being higher than high threshold (h = 1, 1 = 0), smaller than low threshold (h = 0, 1=0) and in between thresholds (h = 0, 1 = 1).

- block 1: First the sum of both currents saved in the two CMCs from block 0 is saved in the first CMC of block 1. Then the same current is saved in the second CMC while the first CMC is evaluated using the two comparators. According to the results the reference current is added, subtracted or disabled in both CMCs. Finally the sum of both CMCs currents is written to the first CMC in block 2. After roughly 20ns the same current is written to the second CMC in block 2.

The procedure for blocks 2, 3 and so forth is the same as described for block 1. The resulting output signal after one block is displayed in figure 4.1 on the right. The final conversion result is D. It is obtained

Figure 4.1: On the left sketch of the pipeline ADC used in this thesis[25]. On the right input signal after a single conversion stage [11].

as follows:  $D = 2^7(h_7 - l_7) + \ldots + 2^0(h_0 - l_0)$ . Therefore the analogue input signal is encoded in one of -255 to 255 digital values. Thus the digital precision of the ADC is given by the number of blocks plus one, with each block adding one bit to the output code and the way the final result is calculated adding another bit. The original signal can be reconstructed with  $I_{signal} = D \frac{R}{128}$  Because further signal processing and data transfer is simplified by encoding the signal with a number of bits which is a power of two (2<sup>x</sup>), the Least significant **B**it (LSB) is discarded. Thus leaving eight bits within the range -127 to 127.

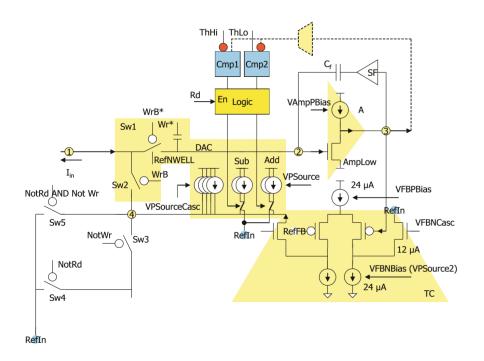

#### 4.1.1 The CMC

The CMC is an essential part of DCDBv3. It is responsible for saving the sampled input signal from the DEPFET. The main components of the CMC are a capacitor, an amplifier and a transconductor. Figure 4.2 shows a circuit diagram of the CMC. To sample the signal from the DEPFET matrix Sw1 (switch 1) is closed and the input current I<sub>in</sub> travels through node number 2 charging the capacitance C<sub>f</sub>. The resulting voltage is stored by opening Sw1. The transconductor (TC in figure 4.2) keeps the voltage across C<sub>f</sub> constant. The stored voltage is fed into the CMP via node 3. There it is compared with the high and low threshold. The high threshold is a current of 7 × IPSource, while the low threshold is  $5 \times IPSource$ . Depending on the result of the comparison a current of (6 × IPSource  $\pm 2 \times IPSource$ ) is added to the stored signal. The current IPSource is a current generated from the voltage VPSource. Then

Figure 4.2: Sketch of the CMC used in the pipeline ADC [25].

the current is fed into the next stage of the ADC.

In chapter 4 the DCD will be optimised. The parameters which are optimised are IPSource, IPSource2, AmpLow and RefIn. These parameters fulfil the following functions:

- **IPSource:** This parameter plays a central role in converting the analogue signal to a digital signal. The thresholds in the CMP and the reference current in the CMC are both derived from IPSource.

- **IPSource2:** Is derived from VPSource2 and among the parameters responsible for the range of input signals the ADC can handle.

- **AmpLow:** Is the ground potential for the transistor used in the amplifier of the CMC. Its main purpose is to lower power consumption by providing a higher ground potential.

Refln: Is the bias voltage and serves as reference potential throughout all ADCs in a DEPFET module.

The IPSource and IPSource2 parameters are important because they influence the DCD performance strongly. But they can be configured for every DCD chip individually. In contrast the RefIn and AmpLow parameters are shared between all DCDs on one module. Thus settings are needed for this parameter which perform well for all DCDs on the ladder.

## 4.2 General analogue to digital conversion

When an analogue signal is converted to a digital signal, information is lost. The reason for this is limited precision. Analogue signals are a continuous range of signals and contain a theoretically unlimited amount of possible values, while a digital representation has a fixed set of discrete values. Thus each increase in digital code by one corresponds to a jump in analogue signal. This smallest increase in

analogue signal which can be described digitally is called LSB.

Ideally the LSB width would remain the same over the whole range of the analogue input signal. This would result in a transfer function with a staircase shape in which each step has the same width and height.

In a real transfer function step size does vary.

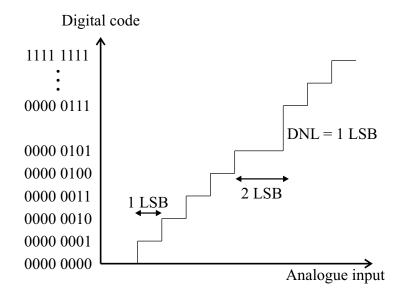

#### 4.2.1 Differential nonlinearity

The **D**ifferential **N**onLinearity (DNL) describes the difference between real step width and ideal step width of one LSB. It is defined as:

$$DNL(i) = \frac{V_{in}(i+1) - V_{in}(i)}{V_{ideal \, LSB}} - 1$$

In this formula  $V_{in}(i)$  represents the input voltage belonging to the digital code *i* and  $V_{in}(i + 1)$  the one belonging to the next larger digital code which occurs (i + 1). The variable  $V_{ideal LSB}$  corresponds to the ideal step width of one LSB. In an ideal analogue to digital converter (ADC) the DNL remains constant at 0 LSB, because the transition values are spaced one LSB apart. The digital output can take a total of  $2^{N}$  values, where N is the number of bits available to encode the output in. The total amount of possible output values is called **full s**cale **r**ange (FSR). If the spacing of transitions is not equal 1 LSB, DNL is

Figure 4.3: Analogue to digital conversion and determination of DNL code.

different from 0 LSB. In figure 4.3 there is a jump from digital code 0000 0101 to 0000 0111. In this ADC the digital code 0000 0110 would never occur. A code which does not occur in the ADC output is called "missing code". Consequently with one less code the FSR would be limited. At the value where the missing code occurs the DNL has a value of 1 LSB. If two digital codes where missing right after each other DNL would take a value of 2 LSB. Consequently DNL can be used to determine how many digital codes are missing and where those codes are missing.

### 4.2.2 Integral nonlinearity

The Integral NonLinearity (INL) describes the deviation of the transfer function from a straight line. There are different approaches how to calculate INL, in this thesis the best straight-line approach was used. In this approach a straight line is fitted to the transfer function. This allows to obtain information on the y-axis intercept (offset) and slope (gain). The INL is determined after both static offset and gain errors have been corrected. It can be calculated with:

$$INL(i) = \left| \frac{V_{in}(i) - V_0}{V_{ideal \ LSB}} - i \right|$$

In this formula  $V_{in}(i)$  represents the analogue value belonging to the digital code *i* and  $V_0$  the minimal analogue value belonging to the digital output code consisting of all zeros. The variable  $V_{ideal LSB}$  corresponds to the ideal step width of one LSB. Summing up all INL values gives the total deviation of the measured ADC curve to the ideal one.

### 4.3 Method of optimisation

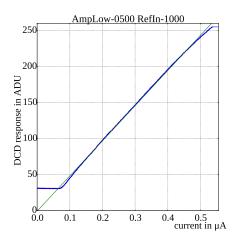

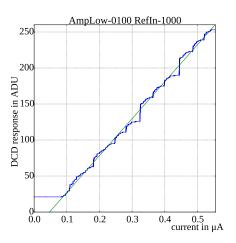

Figure 4.4: Transfer of a test current into digital code.

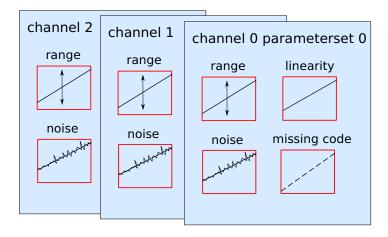

The figure of merit for analogue to digital conversion is the ADC curve, which is measured by feeding a set of known input currents into a DCD channel. Figure 4.4 shows an ADC curve which was measured for close to optimal settings. ADC curves are represented by a 2-dimensional histogram. The x-acis bins show the analogue input while the y-axis bins represent digital output code. ADC curves are tested for quality using four criteria:

- **Range:** The range of ADC values, calculated as largest ADC value minus smallest ADC value contained in fit. This criteria detects limitations to FSR.

- **Linearity:** Linearity of the ADC value's<sup>1</sup> rise with input current, calculated as  $\chi^2_{reduced}$ . This is the representation of INL used in this thesis.

<sup>&</sup>lt;sup>1</sup> ADC values are given in **a**nalogue **d**igital converter **u**nits (ADU).

- **Noise:** How likely the same input current will give rise to the same ADC value, calculated as standard deviation of all ADC values measured at an input current.

- **Missing codes:** Missing codes lead to jumps in the ADC curve. Missing codes are obtained from DNL. In the calculation a code only counts as missing if two or more consecutive ADC codes are missing.

DNL is calculated by summing up how often each ADC code occurs. The occurrence of each ADC code divided by the average occurrence of each ADC code gives the DNL. The calculation for missing codes only considers consecutive missing ADC codes, because a single missing ADC code would not impede operation. To not cut into signal the threshold is usually set more than one ADU lower than the lowest pedestal value of any pixel. Thus a single missing code would, if it was close to the value set as threshold, just function as an additional offset. However, multiple consecutive codes could mask an event which otherwise would be regarded as a hit. To prevent this case of consecutive missing codes an additional test is used. In this test the DNL is checked for large steps. A large DNL step occurs when a lot of successive ADC codes are missing. For the optimisations done in this thesis the test looks for any occurrence of three or more successive missing codes.

To determine the optimal set of IPSource, IPSource2, AmpLow and RefIn parameters multiple scans are conducted. The four parameters are divided into two parameter sets, in each scan one set is investigated. Meaning in each scan two parameters are measured against each other while the remaining parameters are set as constant. These two parameters are scanned over a number of channels. An optimal operating

Figure 4.5: At each configuration a set of tests is conducted. The number of unsuccessful tests over all measured channels is calculated.

point is reached when as many channels as possible show acceptable curves. It is more important for as many channels as possible to work correctly than for individual curves to be as good as possible. Considering that a not functioning channel represents a whole area on the matrix which does not work correctly.

To determine the optimal operating point constraints are defined for each of these tests. The ADC curves of all tested DCD channels are evaluated. A test is counted as passed successfully by a channel if the constraints are met. If the constraints are set too strictly bad DCD channels will be unable to meet the requirements even with their optimal parameter set. If the criteria for passing a test are set too laxly, the optimisation is going to be dominated by bad channels and lots of configurations will show up as

optimal configuration. The values used for the optimisation in this thesis were obtained looking at past measurements, estimating up to what degree we could expect bad channels to perform.

Once one has set a standard for the four tests on range, linearity, noise and missing codes one counts for each combination of parameters how many tests were not passed successfully across all channels (compare to figure 4.5). The algorithm to calculate the optimal operating point searches for the configuration with the lowest amount of tests not passed. Then it checks all parameter combinations to check if there was a test with similarly good results. If there are multiple parameter combinations with close to optimal results, configurations whose parameters are close to the optimal configuration in parameter space are also factored in. These neighbouring configurations are weighted by distance from the ideal configuration. Finally the optimal operating point is the point which passed the most tests or, if there is multiple good points, the one which has the best surroundings. Like the consideration of similar voltages/currents close to the optimal configuration point, the software was designed to also allow additional criteria. One additional criteria which was used for all optimisations in this thesis is additional weight. It is used if all measured DCD channels did not pass a certain test. This weight serves as an insurance to warrant that this configuration is not chosen as the optimal operating point. The criteria used for the tests are summed up in table B.2.

### 4.4 Measurements

After defining the method for optimisation (see section 4.3) the next step is to approach the optimal configuration point with successive measurements. For this thesis scans were done in the IPSource-IPSource2 set and in the AmpLow-RefIn set. The methodology was an iterative approach:

- 1. Conduct a 2D scan for one parameter set.

- Set the parameters which are not scanned to the last obtained optimal values and keep them fixed for the duration of the scan.

- Measure the two parameters in the parameter space in reasonable boundaries.

- Obtain optimal values for the two parameters.

- 2. Conduct a 2D scan in the next parameter space.

- Set the parameters which are not scanned to the last obtained optimal values and keep them fixed for the duration of the scan.

- Measure the two parameters in the parameter space in reasonable boundaries.

- Obtain optimal values for the two parameters.

- 3. Repeat until the values for all the parameters converge or the number of errors hits 0.

For the first scan, as there weren't any measured optimal points yet, the parameters which were not scanned were all set to standard values. Standard values are the ideal values of the last DCD which was optimised. The standard values used in this measurement were obtained during the irradiation campaign in Karlsruhe and they represent stable values which could produce good results throughout the whole irradiation campaign! How these values were obtained and more detailed analysis will be provided in chapter 5.

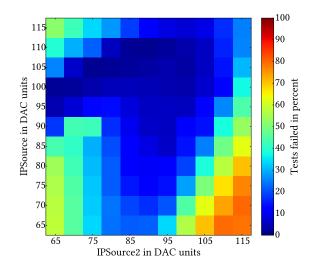

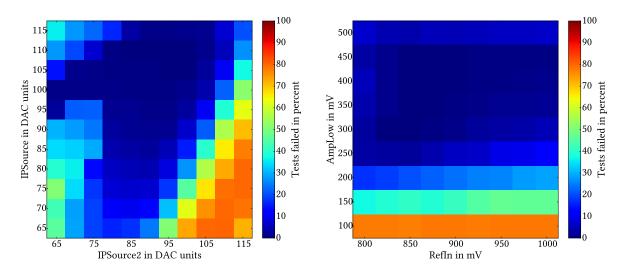

Figure 4.6: Scan in IPSource-IPSource2 parameter space. At each configuration a set of tests is conducted. The number of unsuccessful tests over all measured channels is calculated.

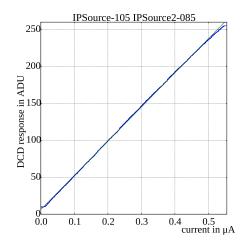

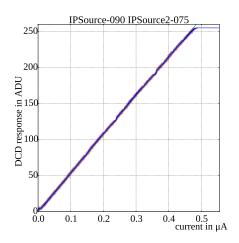

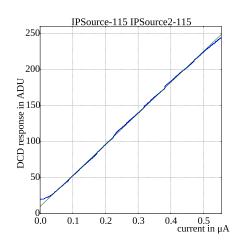

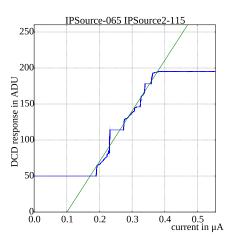

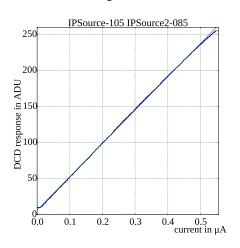

#### 4.4.1 First parameter sweep: IPSource vs IPSource2

The parameter set scanned in the first scan is IPSource- IPSource2. For this scan IPSource is varied between 65 and 115 DAC units in 5 DAC units steps. IPSource2 is varied between 65 and 115 DAC units in 5 DAC units steps. The range for the scan of these parameters was chosen by considering the position of the optimal operating point measured for different DCDs in the past. The optimisation is displayed in figure 4.6. The electronic optimisation calculates the optimal point as:

IPSource = 105 DAC units IPSource2 = 85 DAC units

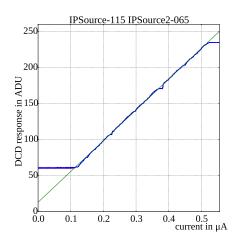

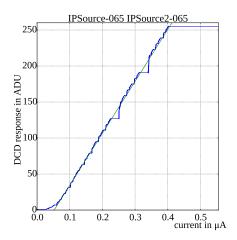

Figure 4.6 shows that the DCD does not work correctly, if IPSource or IPSource2 are chosen too small. Looking at single curves for the bad configurations one observes missing codes. This is displayed in figure 4.9.

If IPSource or IPSource2 are set to large values the ADC curve displays missing codes as shown in figure 4.8.

If IPSource is set to 90 DAC units and IPSource2 is set between 70 and 75 DAC units, strong noise is seen across all channels. This heavy noise is displayed in figure 4.11.

Finally, if one of the parameters IPSource and IPSource2 is too large and the other too small the result is a limited range, refer to figures 4.7 and 4.10 for visualisation.

In conclusion if one or both of the two parameters IPSource or IPSource2 are chosen too large or too small the resulting curves no longer satisfy the standards of the tests. The DCD works best if both IPSource and IPSource2 are close but not the same in value. The optimal configuration is displayed in figure 4.12.

Figure 4.7: Large IPSource and small IPSource2 result in a limited range and missing codes.

Figure 4.9: Small IPSource and small IPSource2 result in missing codes.

Figure 4.11: At certain voltages the noise increases drastically.

Figure 4.8: Large IPSource and large IPSource2 result in missing codes.

Figure 4.10: Small IPSource and large IPSource2 result in a limited range, nonlinearities and missing codes.

Figure 4.12: At the optimal operating point there are no major problems.

#### 4.4.2 Second parameter sweep: AmpLow vs RefIn

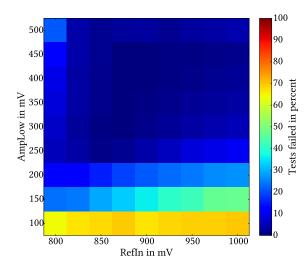

The second parameter space to be scanned is the AmpLow-RefIn parameter set. For this scan the AmpLow voltage is varied between 100 and 500 mV in 50 mV steps. The RefIn voltage is varied between 800 and 1 000 mV in 25 mV steps. These voltages are chosen by considering the position of the optimal operating point determined in previous DCD optimisations. The constraints on the RefIn voltage were set quite tight. The ADC performance is expected to not depend strongly on AmpLow and RefIn. The reason being AmpLow and RefIn are reference potentials which do not play a major role in converting the signal from analogue to digital. Thus the parameter restraints were chosen too tight for curves with strong errors caused by a bad RefIn voltage to appear. The parameter restrains were chosen tight to allow for quick scan times. The optimisation is displayed in figure 4.13. IPSource and IPSource2 were set to the optimal values obtained in the previous scan. Again, the bottom right part of this figure shows the

Figure 4.13: Scan in AmpLow-RefIn parameter space. At each configuration a set of tests is conducted. The number of unsuccessful tests over all measured channels is calculated.

summary of all tests across all measured channels. The software calculates the optimal point as:

$$AmpLow = 400 \text{ mV}$$

$$RefIn = 900 \text{ mV}$$

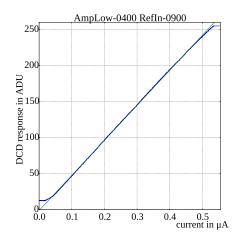

Figures 4.14 to 4.17 show different extreme cases. As reference voltages one would not expect strong dependencies between the two parameters. But some dependencies are visible in figure 4.13. If AmpLow and RefIn are chosen as large values this results in a slightly limited range of the ADC curve and an increase in noise (see figure 4.15).

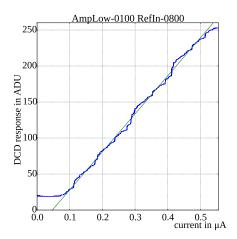

If AmpLow and RefIn are chosen as small values this results in bad linearity of the ADC curve and missing codes (see figure 4.16).

If RefIn is large and AmpLow is small then noise increases (see figure 4.14).

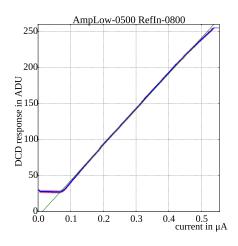

Finally if RefIn is small and AmpLow is large missing codes appear (see figure 4.17). The optimal configuration is displayed in figure 4.18.

Figure 4.14: Small RefIn and large AmpLow result in high noise.

Figure 4.16: Small RefIn and small AmpLow result in missing codes.

Figure 4.18: At the optimal operating point there are no major problems.

Figure 4.15: Large RefIn and large AmpLow result in slightly limited range and increased noise.

Figure 4.17: Large RefIn and small AmpLow result in strong occurrences of missing codes.

### 4.4.3 Iterative parameter scan

The IPSource-IPSource2 and AmpLow-RefIn parameter sets are scanned alternatingly. Also for these scans IPSource is varied between 65 and 115 DAC units in 5 DAC units steps. IPSource2 is varied between 65 and 115 DAC units in 5 DAC units steps. For the AmpLow-RefIn scan the AmpLow voltage is varied between 100 and 500 mV in 50 mV steps. The RefIn voltage is varied between 800 and 1 000 mV in 25 mV steps. The two optimisations are displayed in figures 4.19 and 4.20. Using the electronic

Figure 4.19: Scan in IPSource-IPSource2 parameter Figure 4.20: Scan in AmpLow-RefIn parameter space.

space. AmpLow was set to 400 mV and RefIn to 900 mV. IPSource was set to 105 DAC units and IPSource2 to 95 DAC units.

optimisation on these two scans the optimal points are calculated as:

AmpLow = 400 mVRefIn = 875 mV

Both measurements show multiple points where all tests were successfully passed. The optimal configuration of the IPSource and IPSource2 parameters showed no errors. The configurations directly bordering to this configuration showed any errors in at most 3 (of 64 measured) channels. Making this configuration very stable. In addition, with RefIn voltages between 800 and 1 000 mV and AmpLow voltages between 250 and 450 mV the quality of the analogue to digital conversion is good. Thus a large parameter space is available for optimal settings for RefIn and AmpLow.

# CHAPTER 5

# Irradiation campaign

In the Belle II experiment the PXD will be placed close to the interaction point. Thus the PXD will face strong x-ray radiation. Both the DEPFET sensor the ASICs will need to withstand irradiation of up to 2 Mrad/year (in Si units 20 kGy/year)[20]. It is of great interest how irradiation will influence the ideal working point of the ASICs. Ideally constant tweaking of the operation parameters should be prevented. A set of parameters with which the ASICs perform satisfactorily independent of irradiation should be found. In the March 2016 irradiation campaign in Karlsruhe the DEPFET ASICs were irradiated up to 4 Mrad (in Si units 40 kGy) [26]. This chapter will analyse the behaviour of the DCD under irradiation, using the measurement data from the Karlsruhe campaign. Unless scanned the parameters were set to:

**AmpLow:** 300 mV

Refln: 950 mV

**IPSource:** 90 DAC units

**IPSource2:** 90 DAC units

The rest of the parameters was set to standard values. In the course of the irradiation campaign the device was irradiated first, up to a certain point. Then the parameters AmpLow, RefIn, IPSource and IPSource2 were checked for their optimal value. Also the response of all the channels was measured. To solely observe effects related to the ASICs, no matrix was connected in the Hybrid 5 used for the measurements of this chapter<sup>1</sup>.

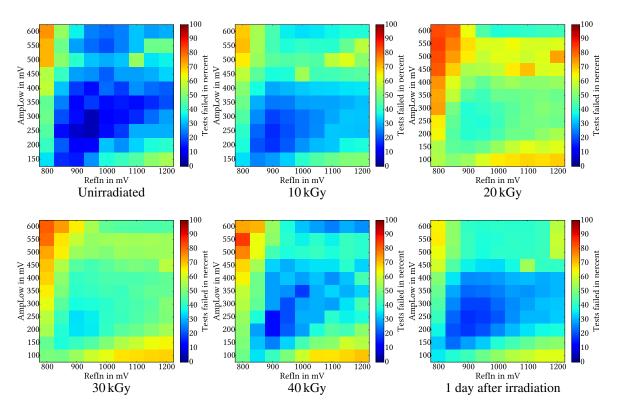

## 5.1 Optimising the AmpLow and Refin parameters

The AmpLow voltage is varied between 100 and 600 mV and the RefIn voltage between 800 and 1 200 mV. The step size and number of channels measured does vary between scans, which is due to time constraints. The measurement data for AmpLow and RefIn is evaluated using the same method which was used in chapter 4. The ideal operation point can be determined when consulting figure 5.1. The figure shows the percentage of tests which were not passed. So a high percentage represents a bad set of parameters. When the DCD is unirradiated there is a wide range of voltages which allow good performance. But as soon as the DCD is irradiated the working area becomes much smaller. As soon as irradiation is increased to 20 kGy or larger there is no configuration where all channels operated

<sup>&</sup>lt;sup>1</sup> ID number of the Hybrid 5 is H5.005.

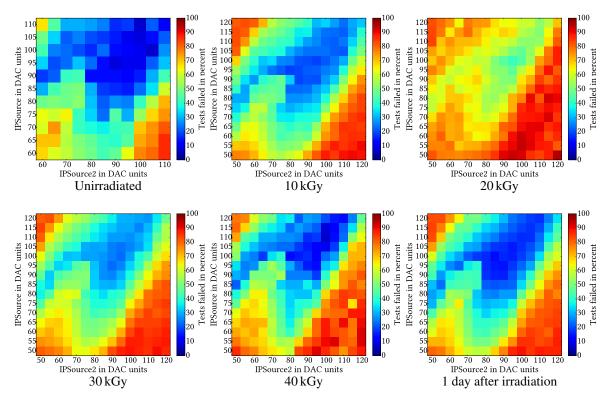

Figure 5.1: Ideal operation point in AmpLow-RefIn plane after different doses. The percentage of tests which were not passed is listed. Blue areas represent good configurations.

flawlessly in all tests. This is in part because the DCD performs worse across all channels with irradiation, but also because in this particular DCD some channels stopped working completely. The cause were communication problems between DCD and DHP, due to failing data links. For a dose of 30 kGy, the DCD does not perform worse than it does for a dose of 20 kGy. When irradiated up to 40 kGy, the DCDs performance increases compared to the measurement at 30 kGy. This behaviour is expected for the type of surface damage the DCD recives and was already observed in previous measurements [20].

The purpose of the tests which are applied to the measured data is to narrow down the voltages the DCD performs best at. Thus the DCD not passing 30 % of the tests does not mean it will not work 30 % of the time. Nevertheless looking at the voltages the DCD performs best at for each irradiation dose, one is able to define voltage ranges in which the DCD performs well for all doses. Varying the RefIn voltage between 850 and 1 000 mV and the AmpLow voltage between 200 and 350 mV gives good results for all doses. After irradiating the DCD up to 40 kGy and then waiting for one day the performance of the DCD is close to the level it was at when the DCD was not yet irradiated.

As AmpLow and RefIn voltage will be shared between all DCDs on one module in the final experiment this working area should overlap with the one measured in chapter 4 in figure 4.20. There is sufficient overlap between the two DCDs and to operate close to optimal settings the RefIn voltage should be between 850 and 1 000 mV and the AmpLow voltage between 250 and 350 mV.

## 5.2 Optimising the IPSource and IPSource2 parameters

The IPSource parameter is varied between 50 and 120 DAC units and the IPSource2 parameter also between 50 and 120 DAC units. As the AmpLow-RefIn optimisation and the IPSource-IPSource2 optimisation were run right after each other, between irradiation steps, the same time constraints apply. Thus step size and number of channels measured does vary between scans. The measurement data for IPSource2 is evaluated using the same method which was used for the AmpLow and RefIn measurement and in chapter 4. Figure 5.2 shows the performance of the DCD for different

Figure 5.2: Ideal operation point in IPSource-IPSource2 plane after different doses. The percentage of tests which were not passed is listed. Blue areas represent good configurations.

doses, depending on IPSource and IPSource2. The unirradiated DCD performs best if both IPSource and IPSource2 are between 85 and 105 DAC units. When the DCD is irradiated the DCD performance worsens with increasing irradiation up to a dose of 20 kGy. When the DCD is irradiated to a dose of 30 kGy or more it starts to recover. After bringing the DCD back to Bonn it recovers to the point of performing similar to an unirradiated DCD after a day.

For optimal performance IPSource and IPSource2 should be larger than 80 DAC units. At the same time there should not be a difference larger than 5 DAC units between the two parameters. A suggestion for an optimal operation point would be setting IPSource to 100 DAC units and IPSource2 to 95 DAC units.

# 5.3 Continuous irradiation

For the last irradiation step from 30 kGy to 40 kGy a number of channels is monitored during irradiation. At set time intervals ADC curves are taken for these channels during irradiation. From these ADC curves

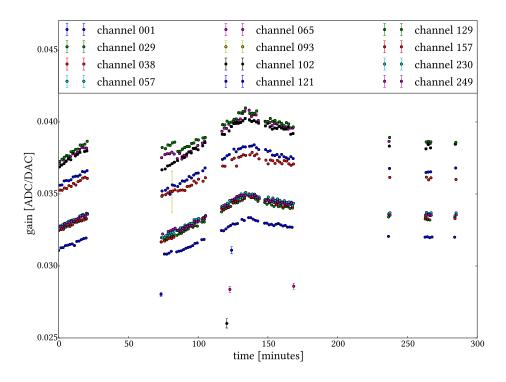

Figure 5.3: Gain measured against time. The DCD is irradiated during the measurements.

gain and noise is extracted for each channel. Figure 5.3 shows how gain changes over time. Up to 25 min gain increases. Then the system was restarted. At 75 min the first measurements after the restart are conducted. Some of the radiation damage to the DCD was already healed by annealing at that point [22]. Hence the gain is slightly lower than before the restart. After 140 min the DCD is no longer irradiated. In conclusion gain increases with increasing dose, after irradiation stops gain decreases over time. Thus an increase in gain with increasing radiation can be expected for the final experiment, as the dose absorbed in in this measurement is equal to half a year of operation at the Belle II experiment.

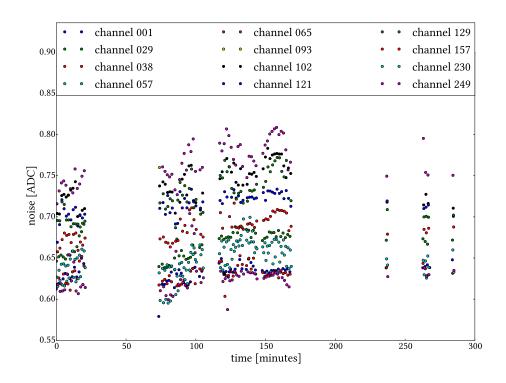

Figure 5.4 shows the same measurements for the same channels over time. For this figure noise was extracted from the measured ADC data. There is no strong increase of noise across the observed doses visible. Noise does increase by 0.01 to 0.02 ADU, but does not decrease after irradiation stops. The cause for this increase could lie in not perfectly stable temperatures. With thresholds set at 4 ADU an increase in noise at this level is unlikely to hinder the experiment. Consequently, considering the radiation levels of 20 kGy/year at the Belle II experiment, a strong increase in noise of the ADC data which stems from the DCD is not expected.

Figure 5.4: Noise measured against time. The DCD is irradiated during the measurements.

# CHAPTER 6

# Gated mode

The goal of the measurements in this section is to understand and verify different aspects of gated mode operation. In section 6.1 the different readout cycles for normal and gated mode operation are explained. Furthermore the system internal timings that are relevant for gated mode operation are measured. In section 6.2 the dead time of the detector is determined. Moreover the ability of gated mode to retain the charge stored within the internal gate is quantified. In addition the ClearLow, ClearHigh and GateOff parameters are optimised for gated mode performance.

# 6.1 Oscilloscope measurements

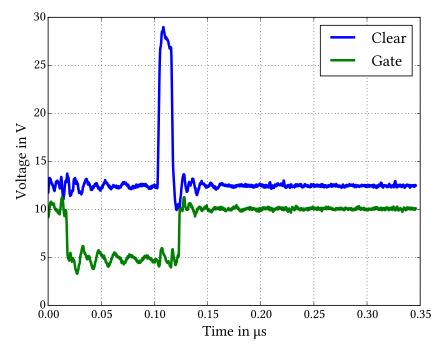

Before the Hybrid 5 board is placed under the laser, the functionality of the Switcher sequences needs to be confirmed and the internal timings measured. To achieve this a Hybrid 5 testboard without matrix is used. The identification of that Hybrid 5 is H5.005. The last two gates of the Switcher were probed and displayed on an oscilloscope.

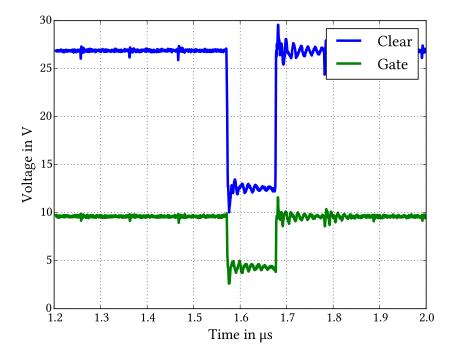

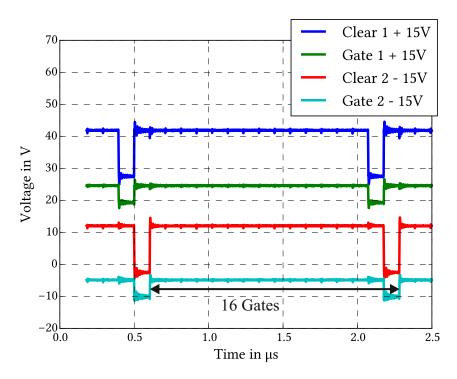

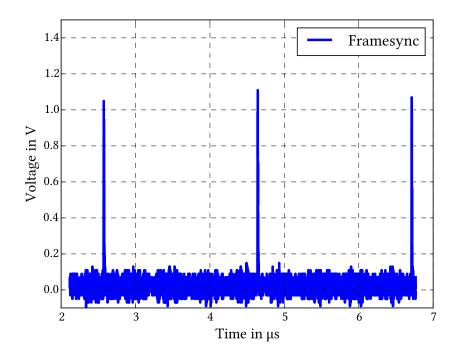

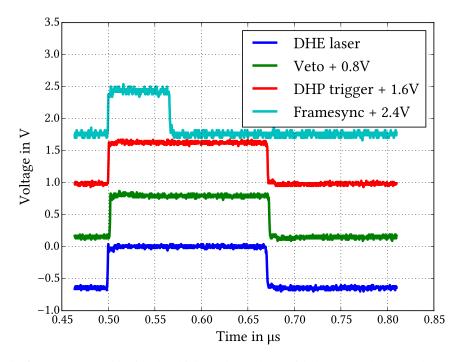

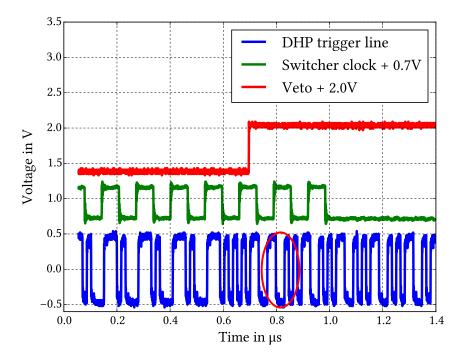

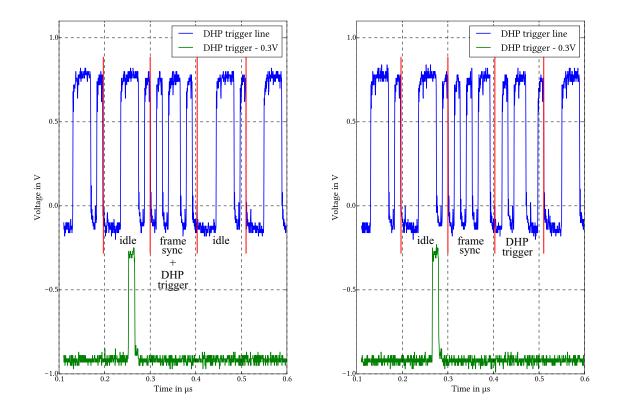

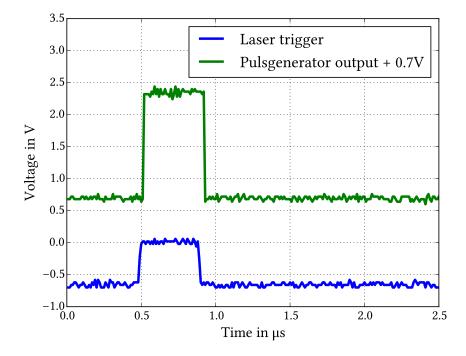

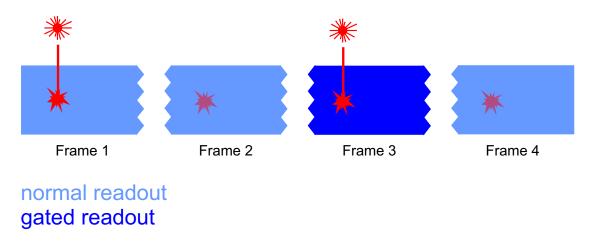

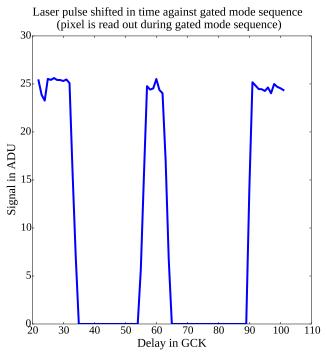

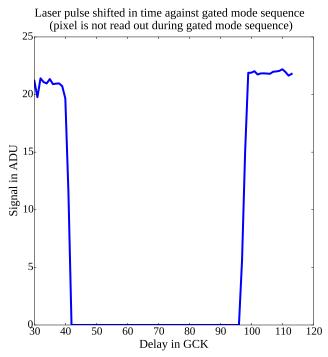

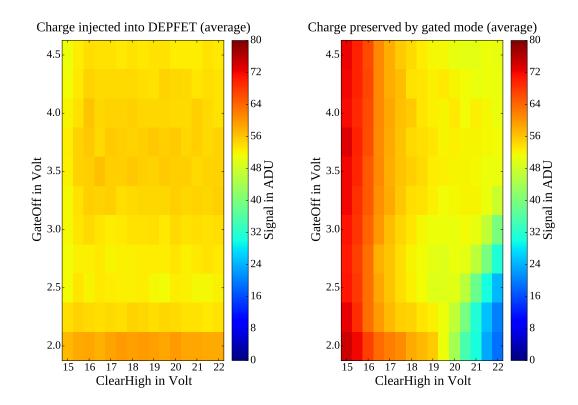

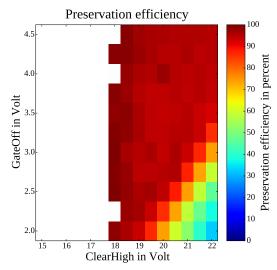

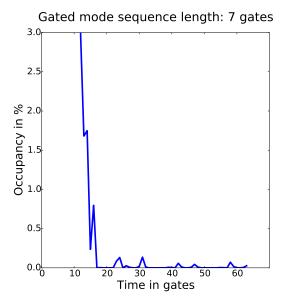

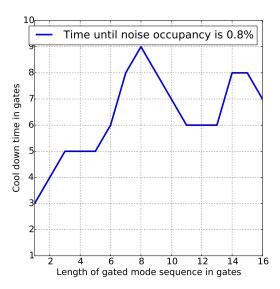

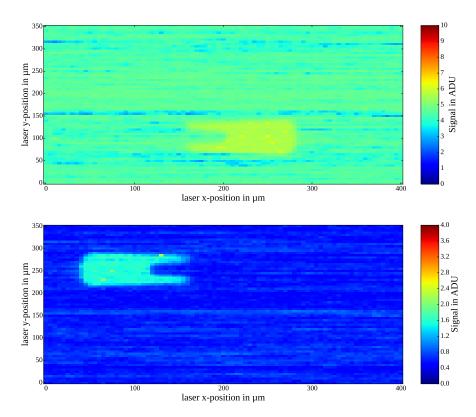

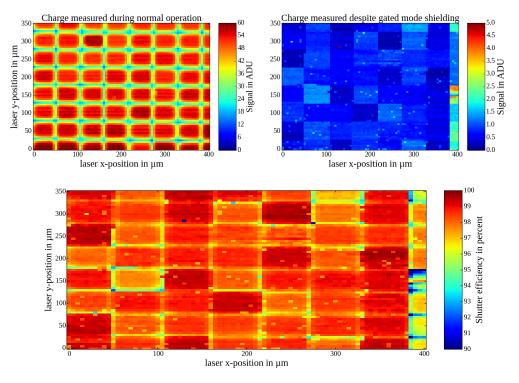

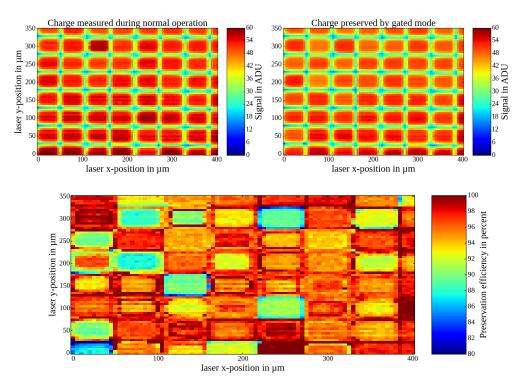

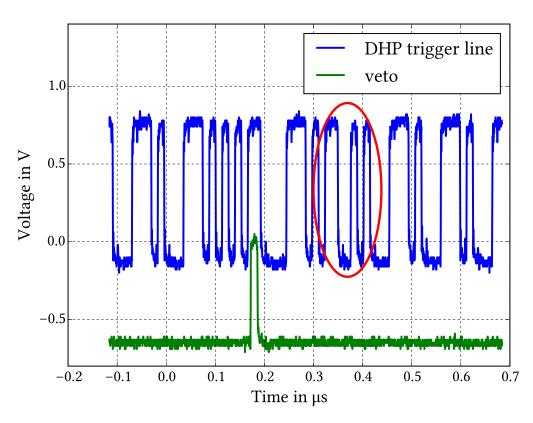

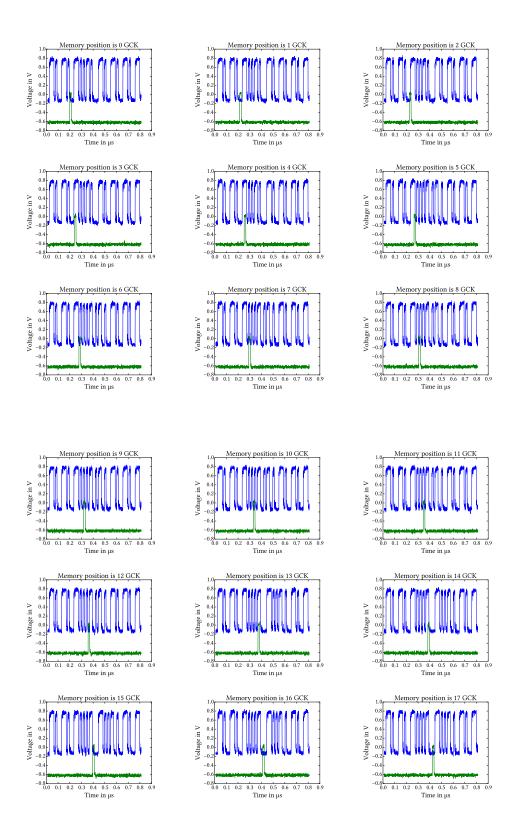

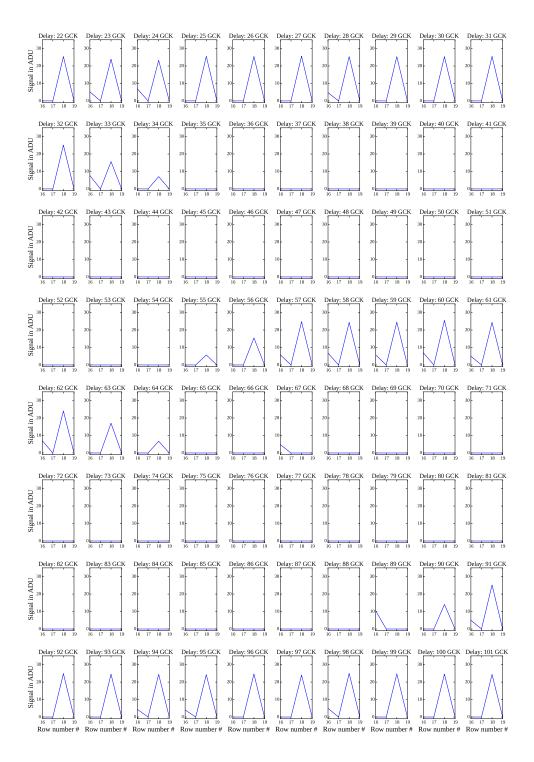

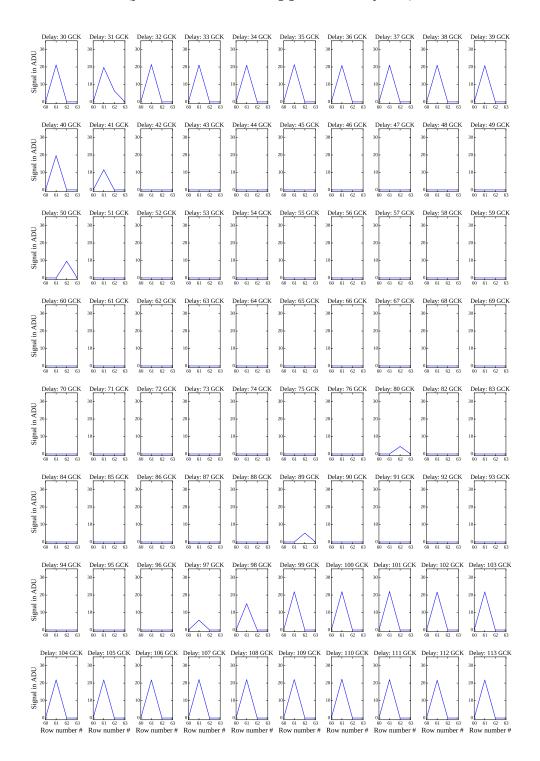

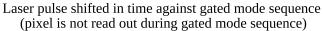

### 6.1.1 Normal readout